ĪĪĪĪ1958─Ļ9į┬12╚šŻ¼Į▄┐╦·╗∙Ā¢▒╚(Jack S.KilbyŻ¼1923-2005)░l├„┴╦╚╦ŅÉÜv╩Ę╔Ž*ēK╝»│╔ļŖ┬ĘŻ¼┤ĄĒæ┴╦╚╦ŅÉ▀M╚ļ“╣ĶĢr┤·”Ą─ĮŪĪŻ1965─ĻŻ¼║ė▒▒░ļī¦¾w蹊┐╦∙į┌ĘŌķ]Ą─ŁhŠ│Ž┬Ż¼ę└┐┐ūį╝║Ą─┴”┴┐Ż¼čąųŲ│╔╣”ę╗ĘN▓╔ė├Įķ┘|Ė¶ļxĄ─DTLą═öĄūųļŖ┬ĘŻ¼ą¹Ėµ┴╦*ēK╣Ķ╗∙öĄūų╝»│╔ļŖ┬ĘĄ─šQ╔·Ż¼ųąć°╝»│╔ļŖ┬Ę«aśIĘŁķ_┴╦Üv╩ĘĄ─ę╗ĒōĪŻ

ĪĪĪĪłDį┤Ż║ųąć°ļŖūėł¾

ĪĪĪĪĮ³60─ĻüĒŻ¼╬ęć°╝»│╔ļŖ┬Ę«aśIÅ─¤oĄĮėąŻ¼ÕøČ°▓╗╔߯¼ūįų„äōą┬Ż¼čąųŲ│÷ę╗┼·ėųę╗┼·Ą─ąŠŲ¼Ż¼ėą┴”ų¦ō╬┴╦╬ęć°ć°├±ĮøØ·║═ć°╝ę░▓╚½Ą─░lš╣ĪŻė╚Ųõ╩Ū╚A×ķ║Ż╦╝Ą─„Ķ„ļ9000ąŠŲ¼Ż¼Ė³╩Ūųąć°ąŠŲ¼Ą─ĄŪĘÕų«ū„ĪŻĄ½╩Ū,į┌├└ć°Į¹┴ŅŽ┬Ż¼ųąć°┼_ĘeļŖ╣½╦Š▓╗į┘×ķ╚A×ķ╣½╦Š┤·╣żąŠŲ¼Ż¼„Ķ„ļ9000ąŠŲ¼╚ńĮ±ęč│╔×ķĮ^│¬ĪŻ─Ū├┤Ż¼─┐Ū░×ķų╣Ż¼¼Fę█Ą─ųąć°*ąŠŲ¼╩Ūį§├┤śėĄ──ž?

ĪĪĪĪę╗Īó¼Fę█ųąć°*ąŠŲ¼

ĪĪĪĪĖ∙ō■“šlų„ÅłŻ¼šl┼eūC”Ą─ęÄätŻ¼▒Š╬─ū„š▀Įo│÷┴╦“¼Fę█ųąć°*ąŠŲ¼”Ą─┼ąöÓęÄätŻ║

ĪĪĪĪ1.įŁät╔Žæ¬įōėąć°═Ōī”ś╦ąŠŲ¼«aŲĘŻ¼Č°▓╗āHāH╩ŪĻPµI╝╝ąg;

ĪĪĪĪ2.├┐─ĻĄ─╚½Ū“╩ął÷Ę▌Ņ~▓╗╔┘ė┌100ā|├└į¬;

ĪĪĪĪ3.ć°«aąŠŲ¼Ą─ąį─▄ģóöĄæ¬įōĮėĮ³Īó▀_ĄĮ╗“š▀│¼▀^ć°═Ōī”ś╦ąŠŲ¼«aŲĘ╦«ŲĮ;

ĪĪĪĪ4.į┌ųąć°┤¾ĻæįOėŗ╝░ųŲįņŻ¼ęčĮø▀M╚ļ╩ął÷Ż¼▓ó╚ĪĄ├õN╩█Ņ~ĪŻ

ĪĪĪĪūŅ║¾Ż¼─▄ØMūŃ╔Ž╩÷4éĆŚl╝■Ą─ųąć°ąŠŲ¼Ż¼─┐Ū░ų╗ėąķLĮŁ┤µā”Ą─3D NANDķW┤µąŠŲ¼X3-9070ĪŻ

ĪĪĪĪČ■ĪóNANDķW┤µąŠŲ¼Ą─ųžę¬╩ął÷Ąž╬╗

ĪĪĪĪ░ļī¦¾w┤µā”Ų„╩Ū╩ŪųĖ═©▀^ī”░ļī¦¾wļŖ┬Ę╝ėęįļŖÜŌ┐žųŲŻ¼╩╣ŲõŠ▀éõöĄō■┤µā”╣”─▄Ą─ąŠŲ¼Ż¼Š▀ėąś╦£╩╗»ĪóÅŖų▄Ų┌Ą╚╠ž³cŻ¼▒╗ĘQ×ķąŠŲ¼ŅIė“Ą─“*ū┌Ą─å╬ę╗«aŲĘ”Ż¼ š╝ō■┴╦ąŠŲ¼┐é╩ął÷Ę▌Ņ~Ą─╝s25%ĪŻ░ļī¦¾w┤µā”Ų„ÅVĘ║æ¬ė├ė┌ėŗ╦ŃÖCĪóöĄō■ųąą─ĪóŠWĮj═©ą┼ĪóŽ¹┘MļŖūėĪóŲ¹▄ćļŖūėĪó╣żśIļŖūėĄ╚ųTČÓŅIė“ĪŻ╦∙ų^Ą─“ėąöĄō■Š═ėą┤µā””!ļSų°╬’┬ōŠWĪó┤¾öĄō■Īó╚╦╣żųŪ─▄Ą─┐ņ╦┘░lš╣Ż¼║Ż┴┐öĄō■ī”░ļī¦¾w┤µā”Ų„Ą─┤µā”├▄Č╚║═öĄō■┐╔┐┐ąį╠ß│÷┴╦Ė³Ė▀ę¬Ū¾ĪŻė╚Ųõ╩ŪŻ¼╣╠æBė▓▒PŽ¹║─┴╦┤¾┴┐Ą─NAND ķW┤µąŠŲ¼ĪŻ

ĪĪĪĪ░ļī¦¾w┤µā”Ų„ų„ę¬░³└©DRAMąŠŲ¼ĪóNAND ķW┤µąŠŲ¼║═NOR ķW┤µąŠŲ¼╚²éĆŽÓī”¬Ü┴óĪóĖ„╦ŠŲõ┬ÜĄ─ŅÉäeĪŻDRAM ║═ NAND FLASH š╝ō■*Ą─ų„ī¦Ąž╬╗ĪŻ╣▓ėŗš╝ō■░ļī¦¾w┤µā”Ų„╩ął÷Ę▌Ņ~Ą─╝s98%ĪŻį┌öĄęį╚fėŗĄ─ąŠŲ¼ĘNŅÉųąŻ¼DRAMąŠŲ¼╩Ū«öų«¤o└óĄ─“ąŠŲ¼ĀŅį¬”ĪŻNANDķW┤µąŠŲ¼Ą─╩ął÷Ę▌Ņ~āH┬įĄ═ė┌DRAMąŠŲ¼Ż¼╩Ū«öų«¤o└óĄ─“ąŠŲ¼░±č█”!ō■ÜWų▐ų¬├¹░ļī¦¾wĘų╬÷ÖCśŗYole░l▓╝Ą─ł¾Ėµ’@╩ŠŻ¼2021─ĻŻ¼NANDķW┤µ╩ął÷Ę▌Ņ~▀_ĄĮ┴╦Į³670ā|├└į¬Ż¼═¼─ĻŻ¼NANDķW┤µ┐é╚▌┴┐ę▓▀_ĄĮ┴╦5855ā|GBĪŻ

ĪĪĪĪNANDķW┤µąŠŲ¼Ą─╩ął÷Ę▌Ņ~ ĪŻłDį┤Ż║Yole

ĪĪĪĪ╚²Īó╩▓├┤╩Ū ŲĮ├µNANDķW┤µąŠŲ¼Ż┐

ĪĪĪĪ1984─ĻŻ¼╚š▒Š¢|ųź╣½╦Š╣ż│╠Ĥ╠┘╬▓į÷ī∙░l├„┴╦ę╗ĘNļŖ┤µā”Įķ┘|ĪŻ╦³─▄į┌ø]ėąļŖį┤Ą─ŪķørŽ┬┤µā”ą┼ŽóŻ¼┐╔ęįīóöĄō■▒Ż┤µ▀_10─Ļęį╔ŽŻ¼▀@Š═╩ŪķW┤µĄ─Ė┼─ŅĪŻ1987─ĻŻ¼╚š▒Š¢|ųź╣½╦ŠčąųŲ│÷┴╦╚½Ū“*ēKNANDķW┤µąŠŲ¼ĪŻŲõ╣żū„įŁ└Ē╩Ūę╗ĘNļŖē║į¬╝■,╗∙ė┌ļŖūė╦Ē┤®ą¦æ¬,īóļŖūėūó╚ļā”┤µå╬į¬ųąĄ─ĖĪäė¢┼śO,Å─Č°Ė─ūāŲõļŖ║╔┴┐,īŹ¼Fą┼Žó┤µā”║═ūx╚ĪĪŻ

ĪĪĪĪ2017─Ļ4į┬¢|ųź┤µā”Ų„╝»łFÅ─¢|ųź╣½╦ŠäāļxŻ¼▓óė┌2019─Ļ10į┬š²╩ĮĖ³├¹×ķKIOXIAŻ¼ųą╬─├¹×ķµzébĪŻ«öŪ░Ż¼µzéb╩ŪāH┤╬ė┌Ēnć°╚²ąŪļŖūė╣½╦ŠĄ─NANDķW┤µąŠŲ¼╔·«aÅS╔╠ĪŻ

ĪĪĪĪNANDķW┤µąŠŲ¼╩Ūę╗ĘNĘŪęū╩¦ąį╝╝ągŻ¼ęįūų╣Ø×ķå╬╬╗▀MąąŠÄ│╠Ż¼ęį“ēK(block)” ×ķå╬╬╗▀Mąą▓┴│²Ż¼öÓļŖ║¾┐╔ķLŲ┌▒Ż│ųą┼Žó,▓┘ū„▓╗ąĶę¬Ė▀ļŖē║▓┘ū„,├┐▒╚╠žĄ─│╔▒ŠĖ³Ą═Ż¼ąį─▄Ė³Ė▀Ż¼│╔×ķĖ▀├▄Č╚öĄō■┤µā”Ą─└ĒŽļ▌d¾wŻ¼ÅVĘ║æ¬ė├ė┌ęŲäė═©ą┼ĪóŽ¹┘MöĄ┤aĪóėŗ╦ŃÖCĪóĘ■äšŲ„╝░öĄō■ųąą─ĪŻ

ĪĪĪĪŠ▀¾wüĒšfŻ¼NANDķW┤µ┐╔ęįļŖ▓┴│²║═ųžą┬ŠÄ│╠ĪŻį┌NANDųąŻ¼öĄō■┤µā”į┌┤µā”å╬į¬ųąŻ¼▓óė╔“0”╗““1”▒Ē╩ŠĪŻę╗éĆå╬į¬┐╔ęį┤µā”├┐éĆå╬į¬1éĆ▒╚╠ž(0Ż¼1)ęį╝░├┐éĆå╬į¬2Īó3║═4éĆ▒╚╠žĪŻį┌╦∙ėąŪķørŽ┬Ż¼╝┤╩╣į┌ŽĄĮyųąĻPķ]ļŖį┤║¾Ż¼öĄō■╚įĢ■▒╗┤µā”ĪŻ

ĪĪĪĪČÓ─ĻüĒŻ¼įōąąśIę╗ų▒╩╣ė├ŲĮ├µNAND╝╝ągĪŻį┌ŲĮ├µNANDųąŻ¼ę╗ŽĄ┴ą┤µā”Ų„å╬į¬čžų°╦«ŲĮ┤«┤«┬ō▀BĮėĪŻé„ĮyĄ─ķW┤µå╬į¬░³└©Š▀ėą┐žųŲ¢┼śO║═ĖĪų├¢┼śOĄ─ŲĮ├µŠ¦¾w╣▄ĮYśŗĪŻ═©▀^Ž“å╬į¬╩®╝ėļŖē║üĒ┤µā”ļŖūė▓óÅ─ĖĪų├¢┼śOęŲ│²ļŖūėĪŻ

ĪĪĪĪŲĮ├µNAND╝╝ągįŁ└ĒĪŻłDį┤Ż║Bing

ĪĪĪĪ30ČÓ─ĻüĒŻ¼═©▀^Ė─▀M╣ż╦ć╝╝ągĪóļŖ┬ĘįOėŗĪóŠÄ│╠╦ŃĘ©║═╣Ō┐╠╝╝ągŻ¼Ė„┤¾ÅS╔╠īóŲĮ├µNANDųąĄ─å╬į¬│▀┤ńÅ─120nmöUš╣ĄĮ1xnm╣سcŻ¼╩╣╚▌┴┐į÷╝ė┴╦100▒ČĪŻ╚╗Č°Ż¼«ö┤µā”å╬į¬ĮYśŗ╠žš„│▀┤ń▀_ĄĮ┴╦15nmĄ─śOŽ▐Ż¼ŲĮ├µNANDķW┤µąŠŲ¼ū▀ĄĮ┴╦▒MŅ^ĪŻŠ▀¾w▒Ē¼F×ķŻ║£ŽĄ└Ą─ōĮļsØŌČ╚ļyęį┐žųŲŻ¼ļSÖCļŖł¾įļ┬Ģ║═ļŖūėūó╚ļĮyėŗöU┤¾┴╦ķōųĄĘų▓╝Ż¼Å─Č°ī¦ų┬Ų„╝■Ą──═Š├ąį║═öĄō■▒Ż│ų╠žąįūā▓ŅĪŻ

ĪĪĪĪļSų°╚╦éāī”╦┘Č╚║═┤µā”╚▌┴┐Ą─ę¬Ū¾įĮüĒįĮĖ▀Ż¼×ķ┴╦╠ßĖ▀┤µā”├▄Č╚Ż¼│²┴╦į┌╣ż╦ć╔Ž▓╗öÓ┐sąĪå╬į¬│▀┤ńŻ¼ęį╠ßĖ▀å╬╬╗├µĘe╔ŽĄ─╝»│╔Č╚═ŌŻ¼Ė³╩Ūį┌ŲĮ├µNAND Ą─╗∙ĄA╔ŽŻ¼░lš╣┴╦3D NANDŻ¼╚▌┴┐ę▓Å─ūŅ│§Ą─4Mbį÷╝ėĄĮ1.33TbŻ¼īŹ¼F┴╦33.3╚f▒ČĄ─į÷ķLĪŻ

ĪĪĪĪ╦─Īó 3DNANDķW┤µąŠŲ¼Ą─░lš╣

ĪĪĪĪ╚ń╔Ž╦∙╩÷Ż¼ŲĮ├µNANDė╔Š▀ėą┤µā”å╬į¬Ą─╦«ŲĮ┤«ĮM│╔ĪŻį┌3D NANDųąŻ¼┤µā”å╬į¬┤«▒╗└Ł╔ņĪóš█»B▓óęį“Uą╬”ĮYśŗ┤╣ų▒žQ┴óĪŻę▓Š═╩ŪšfŻ¼┤µā”å╬į¬╩Ūęį┤╣ų▒ĘĮ╩ĮČč»BĄ─Ż¼īėöĄ┤·▒Ē┴╦Čč»Bį┌ę╗ŲĄ─ūųŠĆĄ─öĄ┴┐Ż¼å╬į¬├▄Č╚ų▒ĮėļSų°Č茯ųąīėöĄĄ─į÷╝ėČ°į÷╝ėŻ¼ūųŠĆīėųąŪąĖŅ│÷ę╗éĆ┤╣ų▒Ą─ų∙ūėĪŻ«öų∙ūė┼c├┐ŚlūųŠĆŽÓĮ╗ĢrŻ¼Š═┤·▒Ē┴╦ę╗éĆ╬’└Ēå╬į¬ĪŻ▀@éĆå╬į¬Š═╩Ūį┌▀@éĆŽÓĮ╗╠Äą╬│╔Ą─ĪŻ

ĪĪĪĪŽ┬łD’@╩Š┴╦3D NANDå╬į¬Ļć┴ą╝▄śŗĪŻūųĘ¹┤«čž┤╣ų▒ĘĮŽ“Ę┼ų├ĪŻūųŠĆ(WL)Š▀ėą░ÕĀŅą╬ĀŅ▓óŪę┤╣ų▒Čč»Bė├ė┌3Då╬į¬Čč»BĪŻį┌ę╗éĆēKĄ─┬®śOé╚(SGD)ėąČÓéĆ▀xō±¢┼śOĪŻNAND┤«Ą─£ŽĄ└Š▀ėąłAų∙¾wą╬ĀŅĪŻ═©▀^╩®╝ėļŖē║Ż¼ļŖūė▒╗Ħ▀M║═Ħ│÷Į^ŠēļŖ║╔┤µā”─żŻ¼ą┼╠¢▒╗ūx╚ĪĪŻ

ĪĪĪĪ3D- NANDķW┤µąŠŲ¼ĪŻłDį┤Ż║░┘Č╚

ĪĪĪĪēK╩Ū▓┴│²▓┘ū„Ą─ę╗éĆå╬į¬Ż¼3D NANDųąėąā╔ĘNŅÉą═Ą─▓┴│²ĘĮĘ©ĪŻĘųäe╩Ū¾w▓┴│²║═GIDL▓┴│²ĪŻ¾w▓┴│²ųąŻ¼NAND┤«▒╗▀BĮėĄĮSięrĄūŻ¼▓óŪę┐šč©▒╗Å─SięrĄū╠ß╣®ĮoNAND┤«Ż¼½@╚Īš²¾wļŖä▌Ż¼īŹ¼F▓┴│²ĪŻį┌GIDL▓┴│²ųąŻ¼NAND┤«┼c╣Ķęr╗∙╚ź±Ņ║ŽŻ¼ą╬│╔N+į┤śOīėĪŻį┌▓┴│²Ų┌ķgŻ¼═©▀^GIDLÖCųŲį┌į┤śO║═┬®śON+ĮY╠Ä«a╔·ļŖūė-┐šč©ī”Ż¼ęįŽ“NAND┤«╠ß╣®┐šč©ĪŻ

ĪĪĪĪ¾w▓┴│²(ū¾)║═GIDL(ėę)▓┴│²Ą─įŁ└ĒĪŻłDį┤Ż║ElectronicsļsųŠ

ĪĪĪĪ2022─Ļ9į┬Ż¼╗∙ė┌CMOSĻć┴ąŽ┬(CuA)╝▄śŗŻ¼╝┤īó NAND Ą─┤¾▓┐Ęų▀ē▌ŗų├ė┌ NAND ┤µā”å╬į¬ų«Ž┬Ż¼├└ć°├└╣Ō╣½╦Š═Ų│÷┴╦╚½Ū“*232īėNANDĪŻ├└╣ŌĄ─232īė NANDīŹ¼F┴╦ėą╩ĘęįüĒūŅĖ▀Ą─├┐ŲĮĘĮ║┴├ūTLC├▄Č╚Ż║14.6Gb/mm2, ▒╚«öĮ±╩ął÷╔ŽĄ─TLCĖéŲĘĖ▀35%ĄĮ100%ĪŻ232īėNAND▓╔ė├ą┬Ą─11.5mmx13.5mmĘŌčb░lžøŻ¼ŲõĘŌčb│▀┤ń▒╚├└╣ŌŪ░Äū┤·«aŲĘąĪ28%ĪŻĖ▀ą¦└¹ė├┴╦ļŖ┬Ę░Õ┐šķgŻ¼Ė³┤¾╚▌┴┐║═Ė³ąĪĘŌčbĄ─ĮY║ŽĖ³▀mė├ė┌Ė„ĘNæ¬ė├ł÷Š░ĪŻ─┐Ū░Ż¼├└╣ŌĄ─232īėNANDęčį┌įō╣½╦ŠĄ─ą┬╝ėŲ┬╣żÅS┴┐«aĪŻÅ─«aŲĘ╗»Ą─ĮŪČ╚üĒ┐┤Ż¼▀@ęŌ╬Čų°├└╣Ō¼Fį┌▀Ć┐╔ęį═©▀^Čč»B 16 éĆ 232īė ┬ŃŲ¼üĒ╔·«a 2TB ┤µā”ąŠŲ¼ĪŻ

ĪĪĪĪ╬ÕĪó 3DNANDķW┤µąŠŲ¼ųŲįņ╝╝ągĄ─╠¶æ

ĪĪĪĪ╚ń║╬ķ_░l│÷│▀┤ńĖ³ąĪĪó╦┘Č╚Ė³┐ņĪó╣”║─Ė³╔┘Īó│╔▒ŠĖ³Ą═Ż¼═¼Ģr╚▌┴┐Ė³┤¾Ą─3D NANDŻ¼ę╗ų▒╩Ū┤µā”ąŠŲ¼ųŲįņ╣ż│╠Ĥ▓╗öÓ├µ┼RĄ─Å═ļs╠¶æĪŻį÷╝ėČč»BīėöĄ*Ą─└¦ļy╩Ū┤_▒ŻČč»BÅ─╔ŽČ°Ž┬Ą─Įyę╗ąįŻ¼▀@ī”ė┌š²┤_ī”²R╦∙ėąĄ─īė║═▀BĮėų∙╩Ū▒ž▓╗┐╔╔┘Ą─Ż¼Š▀¾wüĒšfŻ║

ĪĪĪĪ1)Ė▀┐vÖM▒╚(HAR)┐╠╬g╣ż╦ćŻ¼ęįīŹ¼F╬óąĪĄ─┤╣ų▒£ŽĄ└ĪŻ

ĪĪĪĪ2)į┌┤µā”å╬į¬ų«ķg½@Ą├ūŃē“Ą─“īäėļŖ┴„ĪŻ

ĪĪĪĪ3)CMOSĻć┴ąŽ┬▀ē▌ŗąŠŲ¼įOėŗā×╗»ĪŻ

ĪĪĪĪ4)Š¦łA┬NŪ·ĪŻ

ĪĪĪĪ3D NANDĄ─╝▄śŗėąā╔ĘNŻ¼ę╗ĘN╝▄śŗ╩ŪĒnć°╚²ąŪ╣½╦Š╠ß│÷Ą─å╬īė─Ż╩ĮŻ¼└²╚ńŻ¼╚²ąŪĄ─92īė3D NANDįOéõīó╦∙ėą92īėČč»Bį┌═¼ę╗ąŠŲ¼╔ŽĪŻ╚²ąŪĄ─128īė╝╝ągį┌═¼ę╗ąŠŲ¼╔ŽČč»B128īėĪŻ═©▀^īó╦∙ėą╦∙ąĶĄ─īėČč»Bį┌ę╗éĆąŠŲ¼╔ŽŻ¼ųŲįņ╔╠┐╔ęį£p╔┘│╔▒Š║═ķ_░lĢrķgĪŻĄ½128īėęčĮø╩Ūå╬īė╝▄śŗĄ─śOŽ▐┴╦ĪŻįŁę“╩ŪHAR╬g┐╠╣ż╦ć▓Į¾EĪŻę╗┤╬╬g┐╠128īėĄ─Čč»B─┐Ū░╩Ū┐╔ąąĄ─Ż¼į┘ČÓŠ═▓╗ąą┴╦ĪŻ

ĪĪĪĪ┴Ēę╗ĘN╝▄śŗ╩Ūļpīė─Ż╩ĮĪŻ└²╚ńŻ¼į┌96īėŲ„╝■ųąŻ¼ę╗ą®Ų„╝■īóā╔éĆ48īėĮYśŗČč»Bį┌▒╦┤╦ų«╔ŽĪŻMicronīóā╔éĆ116īėĄ─ĮYśŗČč»Bį┌ę╗ŲŻ¼Å─Č°ą╬│╔232īėĄ─Ų„╝■ĪŻ’@╚╗Ż¼ļpīė─Ż╩Į£p▌p┴╦┐╠╬g╣ż╦ćĄ─ųĖś╦ę¬Ū¾Ż¼Ą½į÷╝ė┴╦Ė³ČÓĄ─▓Į¾E║═│╔▒ŠĪŻ

ĪĪĪĪ3D NANDķW┤µąŠŲ¼ųŲįņ┴„│╠ĪŻłDį┤Ż║Jim Handy, The Memory Guy

ĪĪĪĪ╩ūŽ╚Ż¼į┌╗∙Ąū╔Ž│┴Ęeę╗īė▓─┴ŽŻ¼╚╗║¾į┌Ēö▓┐│┴Ęe┴Ēę╗īė▓─┴ŽĪŻįō▀^│╠ųžÅ═öĄ┤╬Ż¼ų▒ĄĮĮoČ©Ą─Ų„╝■Š▀ėą╦∙ąĶĄ─īėöĄĪŻ├┐éĆ╣®æ¬╔╠Č╝╩╣ė├▓╗═¼Ą─ę╗ĮM▓─┴ŽüĒäōĮ©ę╗ČčīėĪŻ└²╚ńŻ¼į┌╚²ąŪĄ─3D NAND╝╝ągųąŻ¼įō╣½╦Šį┌╗∙░Õ╔Ž│┴ĘeĄ¬╗»╣Ķ║═Č■č§╗»╣ĶĄ─Į╗╠µīėĪŻ

ĪĪĪĪ└Ēšō╔ŽŻ¼╣®æ¬╔╠┐╔ęįČč»B¤oŽ▐öĄ┴┐Ą─īėĪŻĄ½ļSų°Ė³ČÓīėĄ─╠Ē╝ėŻ¼ļy³cį┌ė┌Čč»BŠ▀ėąŠ½┤_║±Č╚║═┴╝║├Š∙ä“ąįĄ─īėĪŻ┤╦═ŌŻ¼«ö│┴ĘeįĮüĒįĮČÓĄ─īėĢrŻ¼▒Ī─żųąĄ─æ¬┴”Ģ■ĘeŠ█ŲüĒŻ¼▀@┐╔─▄Ģ■╩╣Š¦Ų¼┬NŪ·▓ó┼żŪ·łD░ĖĪŻ║¾└m▓╔ė├ļpīė─Ż╩ĮĢrŻ¼ī”£╩Ģ■ūāĄ├Ė³╝ė└¦ļyĪŻ

ĪĪĪĪHAR┐╠╬g╩ŪūŅ└¦ļyĄ─Łh╣ØĪŻ┐╠╬gÖC▒žĒÜÅ─Ų„╝■Čč»BĄ─Ēö▓┐Ń@ĄĮĄū▓┐ęrĄūĄ─╬óąĪłA┐ū╗“═©Ą└ĪŻ═©Ą└╩╣å╬į¬─▄ē“į┌┤╣ų▒Čč»Bųą▒╦┤╦▀BĮėĪŻį┌▀@éĆ▀^│╠ųąŻ¼╩ūŽ╚īó╠╝╗∙▓─┴Ž│┴Ęeį┌»Bīė╔ŽĪŻ▀@ĘN▓─┴Žūā│╔┴╦ę╗éĆłįė▓Ą─č┌▒╬īėĪŻŽ┬ę╗▓Į╩Ūį┌ė▓č┌─ŻĄ─Ēö▓┐ą╬│╔┐ūĄ─łD░ĖĪŻ┐╠╬gÖCęį70:1Ą─┐vÖM▒╚į┌═¼ę╗éĆąŠŲ¼ųą┐╠╬g│÷öĄ░┘╚féĆ╬óąĪĄ─═©Ą└Ż¼├┐éĆ═©Ą└▒žĒÜŲĮąąŪęŠ∙ä“ĪŻ▓óŪęļSų°╬g┐╠╣ż╦ć╔Ņ╚ļ£ŽĄ└Ż¼╬g┐╠╦┘┬╩┌ģė┌ĮĄĄ═ĪŻ┐ūę▓┐╔─▄│÷¼F╠žš„│▀┤ńĄ─ūā╗»ĪŻ

ĪĪĪĪ╩╣ė├Ė„ĘNÖz£y╣żŠ▀£y┴┐å╬═©Ą└ā╚▓┐Ą─Š∙ä“ąį║═▌å└¬ę▓╩Ū└¦ļyĄ─Łh╣ØĪŻĖ³Ė▀Ą─┐vÖM▒╚ĮYśŗīóĦüĒą┬Ą─ĪóĖ³║±Ą─ė▓č┌─Ż║═Ė³īÆĄ─ķgŠÓūųŠĆŻ¼▀Mę╗▓Į╠¶æé„ĮyĄ─Öz£y─▄┴”ĪŻĖ³Ė▀Ą─┐vÖM▒╚£ŽĄ└┐ū║═ūųŠĆĖ¶ļx▀Mę╗▓ĮŽ„╚§┴╦äØŠĆ░ą║═Ų„╝■ĮYśŗų«ķgĄ─ŽÓĻPąįĪŻ▀@ą®æ¬ė├Ą─ėŗ┴┐ąĶę¬▐DęŲĄĮ╣▄ąŠā╚ĪóŲ„╝■╔ŽŻ¼▓ó┼cĖ³Ė▀Ą─ķLīÆ▒╚ĮYśŗŽÓę╗ų┬ĪŻ┴Ē═ŌŻ¼ė├ČÓŠ¦╣Ķ▓─┴Žī”╬óąĪĄ─┤╣ų▒£ŽĄ└▀Mąąā╚ęrŻ¼╚╗║¾ė├č§╗»╬’╠Ņ│õ£ŽĄ└Ż¼ę▓╩Ūę╗éĆļy³cĪŻļSų°┤╣ų▒═©Ą└ūāĄ├įĮüĒįĮĖ▀Ż¼īėįĮüĒįĮČÓŻ¼┤µį┌£ŽĄ└ęŲäėąįĪŻČÓŠ¦╣Ķ£ŽĄ└Ą─▀węŲ┬╩║═┐╔ūāąįį┌║▄┤¾│╠Č╚╔Ž╚ĪøQė┌Š¦┴Ż│▀┤ń║═Ž▌┌Õ├▄Č╚ĪŻ

ĪĪĪĪ┴∙Īóųąć°NANDķW┤µąŠŲ¼Ą─ŅBÅŖß╚Ų

ĪĪĪĪ╣½ķ_┘Y┴Ž’@╩ŠŻ¼2016─Ļ7į┬Ż¼ć°╝ę┤µā”Ų„╗∙ĄžĒŚ─┐į┌╬õØhåóäėŻ¼įōĒŚ─┐ę╗Ų┌║═Č■Ų┌═Č┘Y▀_240ā|├└į¬ĪŻ

ĪĪĪĪ╣½ķ_┘Y┴Ž’@╩ŠŻ¼2016─Ļ12į┬22╚šŻ¼ŪÕ╚AūŽ╣Ō┬ō║ŽŲõ╦¹╣½╦Š╣▓═¼│÷┘Y│╔┴óķLĮŁ┤µā”┐Ų╝╝┐ž╣╔ėąŽ▐ž¤╚╬╣½╦Š(ķLĮŁ┐ž╣╔)Ż¼īŹ¼Fī”ķLĮŁ┤µā”┐Ų╝╝ėąŽ▐ž¤╚╬╣½╦ŠĄ─┐žųŲŻ¼ūŽ╣Ōīó│÷┘Y197ā|į¬│ųėąķLĮŁ┐ž╣╔51.04%╣╔ÖÓĪŻ

ĪĪĪĪķLĮŁ┤µā”┐Ų╝╝ėąŽ▐ž¤╚╬╣½╦ŠŻ¼╝┤ć°╝ę┤µā”Ų„╗∙ĄžŻ¼╩Ūę╗╝ęīŻūóė┌3D NANDķW┤µįOėŗųŲįņę╗¾w╗»Ą─IDM╝»│╔ļŖ┬ĘŲ¾śIŻ¼═¼Ģrę▓╠ß╣®3D NANDķW┤µŠ¦łA╝░Ņw┴ŻŻ¼ŪČ╚ļ╩Į┤µā”ąŠŲ¼ęį╝░Ž¹┘M╝ēĪóŲ¾śI╝ē╣╠æBė▓▒PĄ╚«aŲĘ║═ĮŌøQĘĮ░ĖĪŻ

ĪĪĪĪ2017─Ļ10į┬Ż¼ķLĮŁ┤µā”═©▀^ūįų„čą░l║═ć°ļH║Žū„ŽÓĮY║ŽĄ─ĘĮ╩ĮŻ¼│╔╣”įOėŗųŲįņ┴╦ųąć°*3D NANDķW┤µĪŻ┤“ŲŲć°═Ō░ļī¦¾wÅS╚²ąŪĪóSK║Ż┴”╩┐Īó├└╣ŌĪóėó╠žĀ¢Īó¢|ųźĪó╬„▓┐öĄō■Ą╚Ą─╝╝ągē┼öÓĪŻ

ĪĪĪĪ2019─Ļ9į┬Ż¼┤Ņ▌dķLĮŁ┤µā”ūįų„äōą┬ Xtacking® ╝▄śŗĄ─Ą┌Č■┤·TLC 3D NANDķW┤µš²╩Į┴┐«aĪŻ┼cŲõ╦³ÅS╔╠╝╝ąg▓╗═¼Ż¼ķLĮŁ┤µā”╩ūäōĄ─Xtacking®╝▄śŗį┌ā╔Ņw▓╗═¼Ą─Š¦łA╔ŽųŲįņā╔ĘNļŖ┬ĘŻ¼╚╗║¾į┘▀MąąĘŌčb▀BĮėĪŻŠ═Ž±┤ŅĘe─Šę╗śėŻ¼ūxīæå╬į¬║═┤µā”å╬į¬┐╔ęį¬Ü┴ó╔·«aŻ¼▓╗āHĮĄĄ═╔·«a│╔▒ŠŻ¼▀Ć┤¾┤¾╠ß╔²┴╦ķW┤µąį─▄ĪŻ

ĪĪĪĪ2020─Ļ4į┬Ż¼ķLĮŁ┤µā”ą¹▓╝Ą┌╚²┤·TLC/QLCā╔┐Ņ«aŲĘčą░l│╔╣”Ż¼ŲõųąX2-6070ą═╠¢ū„×ķ*Ą┌╚²┤·QLCķW┤µŻ¼ōĒėą░l▓╝ų«ĢrśIĮńūŅĖ▀Ą─I/O╦┘Č╚Ż¼ūŅĖ▀Ą─┤µā”├▄Č╚║═ūŅĖ▀Ą─å╬Ņw╚▌┴┐ĪŻ

ĪĪĪĪ2022─Ļ8į┬Ę▌Ż¼ķLĮŁ┤µā”š²╩Į░l▓╝200īė+3D NANDķW┤µąŠŲ¼«aŲĘX3-9070Ż¼▀@╩Ū╗∙ė┌Š¦ŚŻ3.0(Xtacking 3.0)╝▄śŗĄ─Ą┌╦─┤·3D TLC NANDķW┤µąŠŲ¼ĪŻķLĮŁ┤µā”╩ūäōĄ─Xtacking 3.0ŽÓ▒╚╔Žę╗┤·«aŲĘŻ¼X3-9070ąį─▄╠ß╔²50%Ż¼╣”║─ĮĄĄ═25%ĪŻ┴Ē═ŌŻ¼įō╝▄śŗ┐╔ęįīŹ¼FĖ▀ą¦Ą─«aŲĘķ_░lą¦┬╩Ż¼║══¼ŅÉÅS╔╠ŽÓ▒╚┤¾╝s─▄£p╔┘3éĆį┬Ą─ķ_░lĢrķgĪŻX3-9070╩Ūųąć°ėą╩ĘęįüĒ┤µā”├▄Č╚ūŅĖ▀Ą─ķW┤µŅw┴ŻŻ¼2022─Ļ12į┬ķ_╩╝▀Mąą┴┐«aĪŻ

ĪĪĪĪąĶę¬ųĖ│÷Ą─╩ŪŻ¼īėöĄ╩ŪķW┤µĄ─ąį─▄ūŅĻPµI╝╝ągųĖś╦Ż¼īėöĄįĮČÓŻ¼å╬╬╗┐šķg┤µā”├▄Č╚Š═įĮ┤¾Ż¼┐é┤µā”╚▌┴┐įĮ╚▌ęū╠ß╔²ĪŻ«ö╚╗Ż¼Įė┐┌╦┘Č╚Īó┐╔┐┐ąįĪóļSÖCūx╚Īąį─▄Īó─▄║─Īó├┐å╬į¬╬╗öĄĄ╚ųĖś╦ę▓║▄ųžę¬ĪŻ

ĪĪĪĪ3D NANDķW┤µąŠŲ¼Ą─┴ó¾wĮYśŗĖ³ę└┘ćė┌┐╠╬gÖC║═╬’└Ē│┴ĘeįOéõŻ¼Č°▓╗╩Ū╣Ō┐╠ÖCüĒīŹ¼FĪŻ«ö╚╗Ż¼╦«Į■ø]╩ĮDUV╣Ō┐╠ÖC╩Ū┴┐«aĖ▀ąį─▄3D NANDķW┤µąŠŲ¼Ą─▒žę¬Ū░╠ßĪŻĄ½╩ŪŻ¼3D NANDķW┤µąŠŲ¼Ą─┴┐«a▓ó▓╗ąĶę¬EUV╣Ō┐╠ÖCĪŻūŻĖŻķLĮŁ┤µā”Ą─200īė+3D NANDķW┤µąŠŲ¼«aŲĘX3-9070!

ĪĪĪĪ╬─š┬ā╚╚▌āH╣®ķåūxŻ¼▓╗śŗ│╔═Č┘YĮ©ūhŻ¼šłųö╔„ī”┤²ĪŻ═Č┘Yš▀ō■┤╦▓┘ū„Ż¼’LļUūįō·ĪŻ

║Żł¾╔·│╔ųą...

║Ż╦ćAIĄ──Żą═ŽĄĮyį┌ć°ļH╩ął÷╔ŽÅV╩▄║├įuŻ¼─┐Ū░šŠā╚└█ėŗ─Żą═öĄ│¼▀^80╚féĆŻ¼║Ł╔wīæīŹĪóČ■┤╬į¬Īó▓Õ«ŗĪóįOėŗĪóözė░Īó’LĖ±╗»łDŽ±Ą╚ČÓŅÉą═æ¬ė├ł÷Š░Ż¼╗∙▒ŠĖ▓╔w╦∙ėąų„┴„äōū„’LĖ±ĪŻ

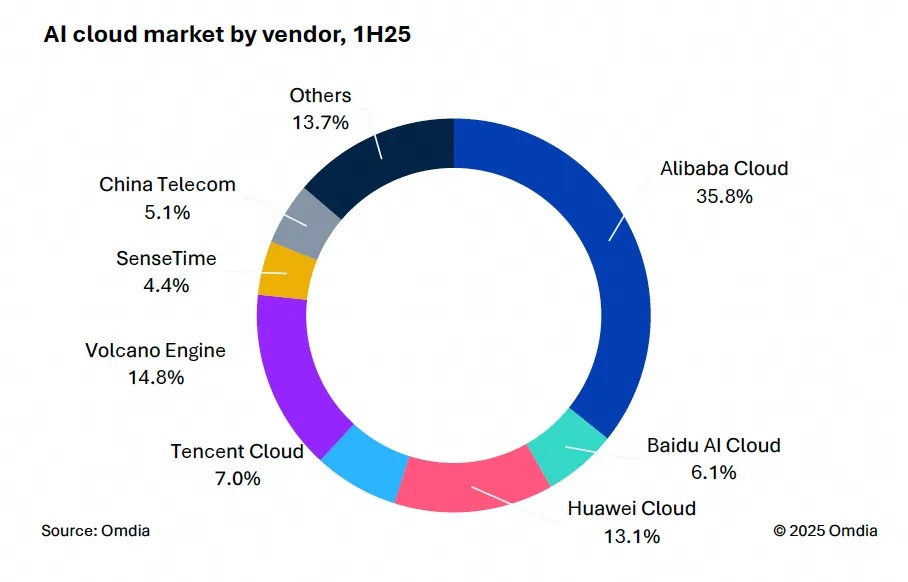

9į┬9╚šŻ¼ć°ļHÖÓ═■╩ął÷š{čąÖCśŗėóĖ╗┬³(Omdia)░l▓╝┴╦ĪČųąć°AIįŲ╩ął÷Ż¼1H25ĪĘł¾ĖµĪŻųąć°AIįŲ╩ął÷░ó└’įŲš╝▒╚8%╬╗┴ąĄ┌ę╗ĪŻ

9į┬24╚šŻ¼╚A×ķ└żņ`š┘ķ_Ī░ųŪ─▄¾w“ׯ¼ę╗Ų┴ĄĮ╬╗Ī▒╚A×ķIdeaHubŪ¦ąą░┘śI¾w“×╣┘ėŗäØ░l▓╝Ģ■ĪŻ

č┼±R╣■ū“╚šą¹▓╝═Ų│÷ā╔┐ŅŅ^┤„╩ĮČ·ÖCŻ¼Ęųäe╩ŪŲĮ░Õš±─żĄ─YH-4000║═äė╚”įŁ└ĒĄ─YH-C3000ĪŻ

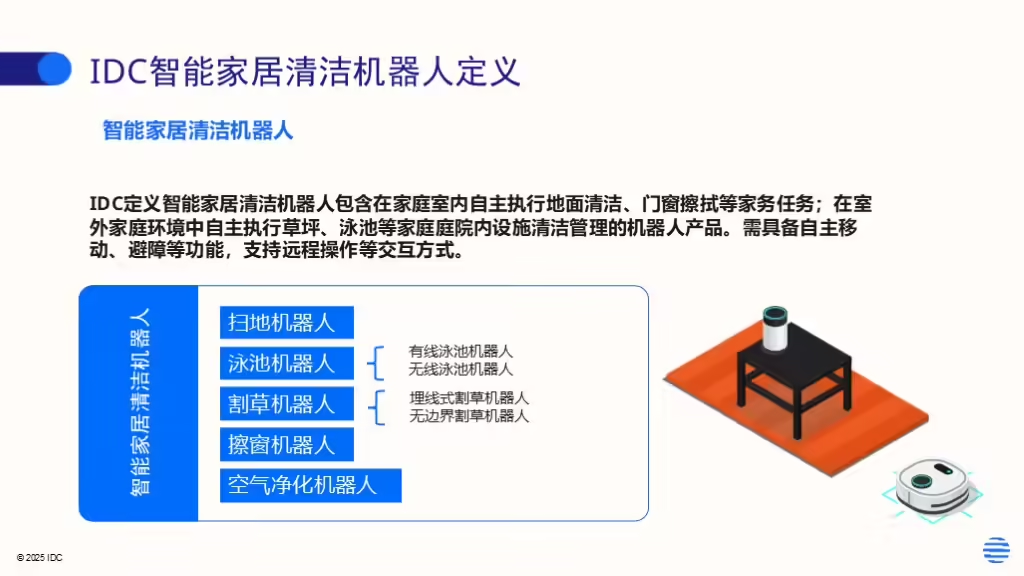

IDCĮ±╚š░l▓╝Ą─ĪČ╚½Ū“ųŪ─▄╝ęŠėŪÕØŹÖCŲ„╚╦įOéõ╩ął÷╝ŠČ╚Ė·█Öł¾ĖµŻ¼2025─ĻĄ┌Č■╝ŠČ╚ĪĘ’@╩ŠŻ¼╔Ž░ļ─Ļ╚½Ū“ųŪ─▄╝ęŠėŪÕØŹÖCŲ„╚╦╩ął÷│÷žø1,2╚f┼_Ż¼═¼▒╚į÷ķL33%Ż¼’@╩Š│÷ŲĘŅÉÅŖä┼Ą─╩ął÷ąĶŪ¾ĪŻ