ĪĪĪĪūŅĮ³Ż¼Ž╚▀M░ļī¦¾w╣ż╦ćųŲ│╠ĘĮ├µĄ─Ž¹Žóėą▓╗╔┘ĪŻŠ═į┌▀^╚źę╗ų▄Ż¼ŽÓĻPĄ─ą┬┬ä░³└©Ż║

ĪĪĪĪ┬ō░l┐Ųą¹▓╝┬╩Ž╚═Ļ│╔3nm╣ż╦ćĄ─Ž┬ę╗┤·SoCĄ─ķ_░lŻ¼┤“ŲŲ┴╦╠O╣¹*╩╣ė├Ž┬ę╗┤·╣ż╦ćųŲįņ╩ųÖCSoCĄ─æT└²

ĪĪĪĪIntel CEOŅAŲ┌īóį┌2025─ĻĮĶų·18A╣ż╦ćüĒūĘ╔Ž╔§ų┴│¼įĮTSMC║═╚²ąŪį┌Ž╚▀MųŲ│╠ŅIė“Ą─*╬╗ų├Ż¼─┐Ū░ęčĮøėą┤¾┐═æ¶ų¦ĖČ┴╦┤¾Ņ~ŅAĖČ┐ŅüĒ╩╣ė├įō╣ż╦ć

ĪĪĪĪIntelŅAėŗīóį┌╬┤üĒā╔─Ļā╚└^└m┤¾┴┐╩╣ė├TSMC╣ż╦ćüĒ╔·«a*▀MĄ─╠Ä└ĒŲ„«aŲĘ(Meteor Lake╝░║¾└m«aŲĘ)Ż¼į┌╬┤üĒā╔─ĻIntel╣└ėŗĢ■╩╣ė├│¼▀^150ā|├└į¬üĒ╩╣ė├TSMCĄ─╣ż╦ć

ĪĪĪĪIntel║═╚²ąŪš²į┌║Žū„ķ_░lŽ┬ę╗┤·ā╚┤µ-╠Ä└ĒŲ„Čč»B«aŲĘ(cache DRAM)Ż¼įō╝╝ągū„×ķī”AMDĄ─3D V-CacheĄ─╗žæ¬Ż¼īóDRAMų▒ĮėČč»Bį┌CPU╔ŽŻ¼Å─Č°┤¾┤¾╠ß╔²ŽĄĮyĄ─╝»│╔Č╚║═ąį─▄

ĪĪĪĪ╚²ąŪį┌├└ć°Ą─4nm╣żÅSŅAėŗį┌2024─ĻĄū═Ļ│╔Ż¼│¼▀^TSMCį┌├└ć°Į©ÅSĄ─╦┘Č╚

ĪĪĪĪÅ─▀@ą®Ž¹ŽóŻ¼╬ęéā┐╔ęį┐┤ĄĮĄ─╩ŪŻ¼╩ūŽ╚Ż¼ļSų°ęį╚╦╣żųŪ─▄×ķų„┴”Ą─ą┬ąĶŪ¾ØuØu═Ųäė░ļī¦¾w╩ął÷ØuØuÅ═╠KŻ¼ī”ė┌Ž╚▀MųŲ│╠«a─▄Ą─ąĶŪ¾ĘŪ│Ż═·╩óŻ¼Č°Š¦łAųŲįņÅSī”ė┌öU┤¾Ž╚▀MųŲ│╠«a─▄ę▓▒¦ų°ĘeśOĄ─æBČ╚ĪŻČ°į┌┴Ēę╗ĘĮ├µŻ¼╚½Ū“ĘČć·ā╚Äū┤¾├ķ£╩Ž╚▀MųŲ│╠Ą─Š▐Ņ^─┐Ū░Ą─ĖéĀÄĖ±Šųę▓║▄ŪÕ│■Ż║TSMC╩ŪŽ╚▀MųŲ│╠ŅIė“Ą─ŅI┼▄š▀Ż¼Ųõ┴╝┬╩║═ąį─▄Č╝─▄*ę╗▓Į▀_ĄĮ▌^Ė▀Ą─╦«£╩Ż¼═¼ĢrTSMC▀ĆōĒėą╚½Ū“*Ą─Ž╚▀MĘŌčb╝╝ągŻ¼ę“┤╦æ{ĮĶ▀@śė*Ą─ŠC║ŽĄž╬╗ŅI┼▄š¹éĆŽ╚▀MųŲ│╠╩ął÷Ż¼┤¾┐═æ¶╝Ŗ╝Ŗį┌TSMCŽ┬å╬ī¦ų┬«a─▄¤oĘ©ØMūŃąĶŪ¾ĪŻ

ĪĪĪĪ╚²ąŪ╩ŪŽ╚▀M╣ż╦ćŅIė“Ą─ėą┴”ĖéĀÄš▀Ż¼ļSų°Ųõ╝╝ąg│╔╩ņČ╚┼cTSMCųØuĮėĮ³ęį╝░TSMC«a─▄ŠoÅłŻ¼╬┤üĒŅAėŗę▓Ģ■½@Ą├Ž╚▀MųŲ│╠ŅIė“Ą─┤¾┴┐ėåå╬ĪŻČ°Intelät╩ŪŽ╚▀M╣ż╦ćŅIė“Ą─ą┬▀MĖéĀÄš▀ĪŻIntelį┌ūŅĮ³▓┼šµš²▀M╚ļŽ╚▀MųŲ│╠Ą─ĖéĀÄėąā╔ųžįŁę“Ż║*╩Ūę“×ķIntelų«Ū░į┌10nm╣ż╦ć╣سcĄ─ķ_░lųą═Žčė┴╦╠½Š├Ż¼ī¦ų┬Ųõ╝╝ągį┌▀^╚źÄū─Ļųą┤¾┤¾┬õ║¾┼cTSMC║═╚²ąŪ;Ą½╩ŪļSų°Pat Gelsinger│╔×ķIntel CEO╬╗ų├║¾▀Mąą┤¾ĄČķ¤Ė½Ą─Ė─Ė’Ż¼─┐Ū░Intelį┌Ž╚▀M╣ż╦ć╝╝ągŅIė“┼cTSMC║═╚²ąŪĄ─▓ŅŠÓęčĮøį┌┐ņ╦┘┐sąĪŻ¼ŅAėŗį┌╬┤üĒā╔─Ļā╚ėąÖCĢ■─▄šµš²║═TSMC/╚²ąŪ═¼▓Į═Ų│÷ūŅą┬╣ż╦ćųŲ│╠ĪŻĄ┌Č■éĆįŁę“╩ŪIntelį┌Pat Gelsingerł╠šŲCEOų«║¾š²╩ĮøQČ©┤¾ęÄ─Ż═Č╚ļŠ¦łA┤·╣żŅIė“Ż¼Å─Č°┼cTSMC║═╚²ąŪšµš²ķ_╩╝ų▒ĮėĖéĀÄ(Č°į┌▀@ų«Ū░Intel▓ó▓╗┤¾ęÄ─Żķ_Ę┼ūį╝ę╣ż╦ćŻ¼ę“┤╦║═TSMC/╚²ąŪ▓óø]ėąų▒ĮėĖéĀÄĻPŽĄ)ĪŻ

ĪĪĪĪ╬ęéāį┌Ž╚▀M░ļī¦¾wųŲ│╠┐┤ĄĮ┴╦śĘė^Ą─╩ął÷ŅAŲ┌║═╗¤ßĄ─ĖéĀÄ;Ą½╩ŪŻ¼į┌ĖéĀÄų«═ŌŻ¼Äū┤¾Š¦łAųŲįņÅSų«ķgę▓ėą║Žū„ĻPŽĄŻ¼▀@Š═ūī▀@ą®╣½╦Šų«ķgĄ─ĻPŽĄūā│╔Ė³╝ė╬ó├ŅĄ─ĖéĀÄ-║Žū„ĻPŽĄĪŻ└²╚ńŻ¼Intel─┐Ū░ūŅų„ę¬CPUśI䚊ĆųąŻ¼▀Ć▒žĒÜę└┐┐TSMCĪŻį┌IntelĄ─Meteor LakeųąŻ¼ŅAėŗGPU tileĢ■╩╣ė├TSMCĄ─╣ż╦ćŻ¼Č°CPUät╩╣ė├Intelūį╝║Ą─╣ż╦ćĪŻ┴Ēę╗ĘĮ├µŻ¼Intelę▓į┌║═╚²ąŪ║Žū„ā╚┤µČč»B╝╝ąg(cache DRAM)ęįūĘ┌sAMDį┌▀@ĘĮ├µĄ─*Ąž╬╗ĪŻ

ĪĪĪĪŽ╚▀MĘŌčbĦüĒĄ─ūā╗»

ĪĪĪĪ▀^╚ź20─ĻķgŻ¼ąŠŲ¼įOėŗąąśIĄ─ų„┴„įOėŗĘČ╩Į╩ŪSoCĪŻSoCįOėŗĘĮĘ©ĮoąŠŲ¼ąąśIĦüĒ┴╦śO┤¾Ą─Ę▒śsŻ¼Ą½╩Ūį┌Ž╚▀MųŲ│╠Ģr┤·Ż¼▀@śėĄ─įOėŗĘĮĘ©Ģ■ė╔ė┌Ž╚▀MĘŌčb╝╝ągČ°░l╔·Ė─ūāŻ¼Č°▀@śėĄ─Ė─ūāę▓Ģ■ī”Ž╚▀MųŲ│╠Š¦łAųŲįņÅSĄ─ĖéĀÄ║Žū„ĻPŽĄÄ¦üĒĖ─ūāĪŻ

ĪĪĪĪį┌SoCįOėŗĘĮĘ©ųąŻ¼SoCąŠŲ¼ė╔įSČÓIPĮM│╔ĪŻąŠŲ¼įOėŗ╣½╦Šį┌įOėŗSoCĢrŻ¼╩ūŽ╚Č©┴xąĶę¬SoC╔ŽąĶꬥ─IPŻ¼▓óŪęÅ─Ą┌╚²ĘĮIP╠ß╣®╔╠╠Ľ@╚ĪIP╗“š▀ūį╝║įOėŗIP;╚╗║¾░č▀@ą®IP╝»│╔ĄĮąŠŲ¼╔ŽŻ¼ūŅ║¾░čš¹éĆSoC╦═ĄĮŠ¦łAųŲįņÅSųą▀Mąą┴„Ų¼ųŲįņĪŻ

ĪĪĪĪį┌SoCįOėŗĘĮĘ©ųąŻ¼ąŠŲ¼įOėŗ╣½╦ŠĖ³ČÓĄ─╩ŪĻPūóSoCŽĄĮyęį╝░├┐éĆIPĄ─įOėŗŻ¼Ą½╩Ūį┌ąŠŲ¼ųŲįņĄ─Ģr║“Ż¼╦∙ėąĄ─IPČ╝Ģ■╩╣ė├═¼śėĄ─╣ż╦ć╚źųŲįņŻ¼Č°▓╗┐╔─▄ī”ė┌▓╗═¼Ą─IP╩╣ė├▓╗═¼Ą─╣ż╦ć╚źųŲįņĪŻ

ĪĪĪĪČ°ļSų°Ž╚▀M╣ż╦ć║═Ž╚▀MĘŌčbĄ─░lš╣Ż¼▀@śėĄ─SoCįOėŗĘĮĘ©š²į┌┬²┬²▒╗ąŠŲ¼┴Ż(chiplet)įOėŗĘĮĘ©╚Ī┤·ĪŻŽ╚▀M╣ż╦ćĄ─│╔▒Š║▄Ė▀Ż¼┴╝┬╩ģs▓ó▓╗╚▌ęūū÷Ė▀Ż¼×ķ┴╦╠ßĖ▀┴╝┬╩Ż¼═©│ŻĄ─ĘĮĘ©╩Ū░č┤¾ąŠŲ¼Ęų│╔ČÓéĆąŠŲ¼┴ŻŻ¼▓óŪę╩╣ė├Ė▀╝ēĘŌčb╝╝ągū÷ąŠŲ¼┴Żų«ķgĄ─š¹║ŽĪŻ─┐Ū░Ż¼AMDĪóIntelĄ╚Č╝ęčĮøį┌ūŅą┬Ą─╠Ä└ĒŲ„«aŲĘųą╩╣ė├▀@śėĄ─ąŠŲ¼┴ŻįOėŗŻ¼ŅAėŗ╬┤üĒąŠŲ¼┴ŻįOėŗīóĢ■│╔×ķĖ³ČÓ╩╣ė├Ž╚▀MųŲ│╠Ą─┤¾ą═ąŠŲ¼Ą─▀xō±ĪŻ

ĪĪĪĪČ°ę╗Ą®SoCįOėŗĘĮĘ©┬²┬²▒╗ąŠŲ¼┴ŻįOėŗĘĮĘ©╦∙╚Ī┤·Ż¼SoCįOėŗĘĮĘ©ųą“š¹éĆSoCČ╝ę¬╩╣ė├ŽÓ═¼░ļī¦¾w╣ż╦ćųŲįņ”Ą─╝┘įOę▓Š═▓╗į┘│╔┴óŻ¼ę“┤╦├┐ę╗éĆąŠŲ¼┴ŻČ╝┐╔ęį╩╣ė├▓╗═¼Ą─╣ż╦ćüĒųŲįņĪŻš²╚ń2015─ĻMarvellį┌ISSCC╔Ž╠ߥĮĄ─MoChiĖ┼─Ņę╗śėŻ¼š¹éĆ╗∙ė┌ąŠŲ¼┴ŻĄ─įOėŗ░čš¹éĆąŠŲ¼ŽĄĮy▓Ęų│╔┴╦ČÓéĆąŠŲ¼┴ŻŻ¼├┐éĆąŠŲ¼┴ŻČ╝┐╔ęį╩╣ė├ūŅ▀m║ŽĄ─╣ż╦ćüĒųŲįņŻ¼▓óŪęūŅĮKš¹║Žį┌ę╗ŲĪŻ

ĪĪĪĪ╬ęéāį┌IntelĄ─Meteor LakeųąŠ═┐┤ĄĮ┴╦▀@śėĄ─įOėŗĪŻį┌Meteor LakeųąŻ¼Ęų│╔┴╦ČÓéĆąŠŲ¼┴Ż(IntelĘQų«×ķ“tile”)Ż¼░³└©CPU TileŻ¼GPU TileŻ¼SOC Tile║═IO TileĄ╚Ż¼▀@ą®▓╗═¼Ą─TileČ╝┐╔ęįė├▓╗═¼Ą─╣ż╦ćųŲįņ▓óŪęūŅ║¾╩╣ė├Ė▀╝ēĘŌčb╝╝ąg╝»│╔į┌ę╗ŲĪŻį┌Meteor LakeųąŻ¼CPU Tile╩╣ė├IntelĄ─╣ż╦ćŻ¼Č°GPU TileätĢ■╩╣ė├TSMCĄ─╣ż╦ćĪŻ

ĪĪĪĪ▓Ņ«É╗»īó╩Ū╬┤üĒč▌╗»ĘĮŽ“

ĪĪĪĪ«ö╩╣ė├Ž╚▀M╣ż╦ćĄ─ąŠŲ¼įOėŗĘĮĘ©ųØuÅ─SoC▐DŽ“ąŠŲ¼┴ŻŻ¼Š¦łAųŲįņÅS╬┤üĒĄ─ėåå╬ę▓┐╔═¹ųØuÅ─š¹éĆSoC┬²┬²▐DŽ“å╬¬ÜĄ─ąŠŲ¼┴ŻĪŻąŠŲ¼įOėŗÅS╔╠┐╔ęį▀xō±ūŅ▀m║ŽĄ─Š¦łAųŲįņÅS╚źųŲįņŽÓæ¬Ą─ąŠŲ¼┴Ż▓óŪęūŅ║¾╝»│╔ĄĮę╗ŲĪŻąŠŲ¼┴ŻįOėŗĘĮĘ©╝ė╔ŽŽ╚▀M╣ż╦ćūį╔ĒĄ─╠žąįŻ¼┐╔─▄Ģ■ūī╬┤üĒŠ¦łAųŲįņÅSįĮüĒįĮīŻūóė┌▓Ņ«É╗»ĪŻ

ĪĪĪĪŽ╚▀MųŲ│╠║▄┘FŻ¼Ą½╩ŪĦüĒĄ─ąį─▄╠ß╔²▓ó▓╗┤¾ĪŻį┌Š┼╩«─Ļ┤·─”Ā¢Č©┬╔Ą─³SĮĢr┤·Ż¼├┐┤╬╣ż╦ć╣سc┐sąĪČ╝┐╔ęįīŹ¼FŠ¦¾w╣▄ąį─▄Äū║§ĘŁ▒Č;Č°į┌─┐Ū░Ż¼├┐ę╗┤·╣ż╦ćč▌▀MĦüĒĄ─Š¦¾w╣▄ąį─▄╠ß╔²āHāHį┌10-20%ū¾ėęĪŻ┐╔ęįŽļŽ±Ż¼ąŠŲ¼įOėŗ╣½╦Šį┌┤¾│╔▒Š═Č╚ļŽ╚▀M╣ż╦ćųŲįņąŠŲ¼║¾Ż¼ę▓▒ž╚╗ŽŻ═¹▀@śėĄ─Ė▀═Č╚ļ─▄½@Ą├▒M┐╔─▄┤¾Ą─╗žł¾Ż¼ę“┤╦ŽŻ═¹┐╔ęįį┌ąŠŲ¼┴ŻĄ─Ņw┴ŻČ╚╔ŽīŹ¼F├┐éĆąŠŲ¼┴ŻĄ─ąį─▄*ĪŻ

ĪĪĪĪČ°į┌┴Ēę╗ĘĮ├µŻ¼ė╔ė┌Ž╚▀M╣ż╦ćčą░lļyČ╚Š▐┤¾Ż¼Ūęčą░l│╔▒Š═Č╚ļŠ▐┤¾Ż¼ę“┤╦▓╗╠½┐╔─▄│÷¼Fę╗╝ꊦłAųŲįņÅSį┌ąį─▄Īó╣”║─Īó│╔▒ŠĄ╚ŅIė“╚½ĘĮ╬╗┤¾Ę∙*Ųõ╦¹Š¦łAųŲįņÅSĄ─ŪķørŻ¼Ė³ėą┐╔─▄╩Ūį┌▓╗═¼Ą─įOėŗŅIė“Ż¼▓╗═¼Ą─Š¦łAÅSĖ„ėą╦∙ķLŻ¼Å─Č°īŹ¼F▓Ņ«É╗»ĖéĀÄĪŻ▀@└’Ą─▓Ņ«É╗»Ż¼╝╚░³└©┴╦į┌ąį─▄Īó╣”║─Īó│╔▒ŠĄ╚ųĖś╦ŠSČ╚Ą─ģ^äe;ę▓░³└©┴╦▓╗═¼Ą─ÅS╔╠╔├ķL▓╗═¼ŅIė“Ą─ąŠŲ¼┴ŻŻ¼└²╚ńTSMC╔├ķLĖ▀ąį─▄ėŗ╦ŃŻ¼╚²ąŪ╔├ķL┤µā”ŽÓĻPŅIė“Ą╚ĪŻ

ĪĪĪĪį┌▀@śėĄ─ŪķørŽ┬Ż¼▓╗═¼Š¦łAÅS▓Ņ«É╗»ĖéĀÄŻ¼Č╝Ė„ėąūį╝║╔├ķLĄ─ĘĮŽ“Ż¼Č°ąŠŲ¼įOėŗ╣½╦ŠätĖ„╚Ī╦∙ķLŻ¼╩╣ė├▓╗═¼Ą─Š¦łAųŲįņÅS╚źū÷ūŅ╔├ķLŅIė“Ą─ąŠŲ¼┴Ż▓óŪęūŅ║¾š¹║Žį┌ę╗ŲŻ¼┐╔─▄Š═╩Ū╬┤üĒĄ─ą┬ĖéĀÄĖ±ŠųĪŻIntelĄ─Meteor LakeųąŻ¼GPU Tile╩╣ė├TSMCųŲįņŻ¼Š═╩Ūę“×ķTSMC╔├ķLĖ▀ąį─▄ėŗ╦ŃąŠŲ¼┴Ż;Č°CPU Tile╩╣ė├IntelĄ─╣ż╦ćųŲįņŻ¼ę▓╩Ūę“×ķIntelį┌CPUŅIė“Ą─╣ż╦ć-ąŠŲ¼ģf═¼įOėŗėąų°Äū╩«─ĻĄ─Ęe└█ĪŻ╬┤üĒMeteor Lake▀@śėĄ─▓╗═¼Š¦łAÅSųŲįņ▓╗═¼ąŠŲ¼┴Ż┐╔═¹Ģ■│╔×ķų„┴„Ż¼Č°▀@ę▓Ģ■ūīŠ¦łAÅSū▀▓Ņ«É╗»ĖéĀÄĄ─Ą└┬ĘĪŻ

ĪĪĪĪŽ╚▀MĘŌčbīó╩ŪŽ╚▀MųŲ│╠Ėé┘ÉųąĄ─

ĪĪĪĪ║╦ą─ĖéĀÄ┴”

ĪĪĪĪ╚ńŪ░╦∙╩÷Ż¼ąŠŲ¼┴ŻįOėŗĘĮĘ©īó┤¾┤¾Ė─ūāŠ¦łAųŲįņÅSį┌Ž╚▀MųŲ│╠ŅIė“Ą─ĖéĀÄĖ±ŠųŻ¼Č°į┌╔Ž╩÷Ęų╬÷ųąŻ¼▓╗æ¬║÷ęĢĄ─╩ŪŽ╚▀MĘŌčb╝╝ągę▓īó│╔×ķę╗éĆųžę¬ūā┴┐Ż¼ę“×ķŽ╚▀MųŲ│╠ąŠŲ¼(ė╚Ųõ╩ŪĖ▀ąį─▄ėŗ╦ŃąŠŲ¼)ļx▓╗ķ_Ž╚▀MĘŌčb╝╝ągĪŻČ°ŪęĖ³ĻPµIĄ─╩ŪŻ¼Ž╚▀MĘŌčb╝╝ągį┌╬┤üĒīóĢ■║═Ž╚▀MųŲ│╠įĮüĒįĮŠo├▄ĄžĮY║ŽŻ¼Č°šŲ╬š▀@ą®Ž╚▀MĘŌčb╝╝ągĄ─ę▓ŪĪŪĪ╩ŪTSMCĪóIntel║═╚²ąŪ▀@śėĄ─Ž╚▀MųŲ│╠Š¦łAųŲįņÅSŻ¼Č°▓╗╩ŪĄ┌╚²ĘĮĘŌ£yÅSĪŻ

ĪĪĪĪį┌╬┤üĒŻ¼Ž╚▀MĘŌčbĄ─ųžę¬ąį╔§ų┴▓╗üåė┌Ž╚▀MųŲ│╠Ą─ā×╗»─▄┴”Ż¼╬┤üĒĄ─Š¦łAųŲįņÅSĖéĀÄ┴”īóĢ■╚ĪøQė┌░ļī¦¾w╣ż╦ć║═Ž╚▀MĘŌčb╝╝ągĄ─ŠC║ŽĪŻ└²╚ńŻ¼─┐Ū░TSMC─▄½@Ą├Nvidia *** GPUėåå╬Ą─ę╗éĆųžę¬ę“╦žŻ¼Š═╩Ūę“×ķTSMC═¼ĢrōĒėą*▀MĄ─4nm░ļī¦¾wųŲįņ╣ż╦ćęį╝░CoWoSŽ╚▀MĘŌčb╝╝ągŻ¼Č°─┐Ū░***╣®▓╗æ¬Ū¾╩┬īŹ╔Ž╩Ū▒╗CoWoS«a─▄╦∙Ž▐ųŲŻ¼Č°▓╗╩Ū4nm░ļī¦¾w╣ż╦ć«a─▄╦∙Ž▐ųŲĪŻ╩┬īŹ╔ŽŻ¼ė╔ė┌Ž╚▀MĘŌčb║═Ž╚▀MųŲ│╠╣®žø╔╠╗źŽÓųž║ŽŻ¼Š¦łAųŲįņÅS╔§ų┴ėą┐╔─▄└¹ė├Ųõį┌─│ę╗ĘĮ├µĄ─ā×ä▌üĒŪ╦äė╩ął÷(└²╚ńŻ¼└¹ė├Ųõį┌Ž╚▀MĘŌčbŅIė“Ą─ā×ä▌üĒÅøčaŲõį┌─│éĆŅIė“Ž╚▀MųŲ│╠╔ŽĄ─┴ėä▌üĒ½@Ą├ėåå╬)ĪŻ

ĪĪĪĪš╣═¹╬┤üĒŻ¼TSMC─┐Ū░ļm╚╗═¼ĢrōĒėąŽ╚▀MĘŌčb║═Ž╚▀M╣ż╦ćĘĮ├µĄ─*Ąž╬╗Ż¼Ą½╩ŪIntelį┌EMIBĄ╚Ž╚▀MĘŌčb╝╝ąg╔ŽęčĮøėą║▄Š├Ą─╝╝ągĘe└█Ż¼ļSų°Intelį┌Ž╚▀M░ļī¦¾w╣ż╦ćūĘ┌sŻ¼╬┤üĒā╔š▀ĮY║ŽĢ■ėąŽÓ«öĄ─ĖéĀÄ┴”;Č°SamsungĄ─I-Cube/H-Cube║═X-CubeĄ╚Ž╚▀MĘŌčb╝╝ąg┐╔═¹ę▓Ģ■į┌SoC/ā╚┤µ╝»│╔ŅIė“ėąūį╝║¬Ü╠žĄ─ā×ä▌ĪŻ╬┤üĒĄ─Ž╚▀M╣ż╦抦łAÅSų«ķgĄ─ĖéĀÄĖ±Šų▀h╬┤ēm░Ż┬õČ©Ż¼ųĄĄ├╬ęéāĻPūóĪŻ

ĪĪĪĪ╬─š┬ā╚╚▌āH╣®ķåūxŻ¼▓╗śŗ│╔═Č┘YĮ©ūhŻ¼šłųö╔„ī”┤²ĪŻ═Č┘Yš▀ō■┤╦▓┘ū„Ż¼’LļUūįō·ĪŻ

║Żł¾╔·│╔ųą...

║Ż╦ćAIĄ──Żą═ŽĄĮyį┌ć°ļH╩ął÷╔ŽÅV╩▄║├įuŻ¼─┐Ū░šŠā╚└█ėŗ─Żą═öĄ│¼▀^80╚féĆŻ¼║Ł╔wīæīŹĪóČ■┤╬į¬Īó▓Õ«ŗĪóįOėŗĪóözė░Īó’LĖ±╗»łDŽ±Ą╚ČÓŅÉą═æ¬ė├ł÷Š░Ż¼╗∙▒ŠĖ▓╔w╦∙ėąų„┴„äōū„’LĖ±ĪŻ

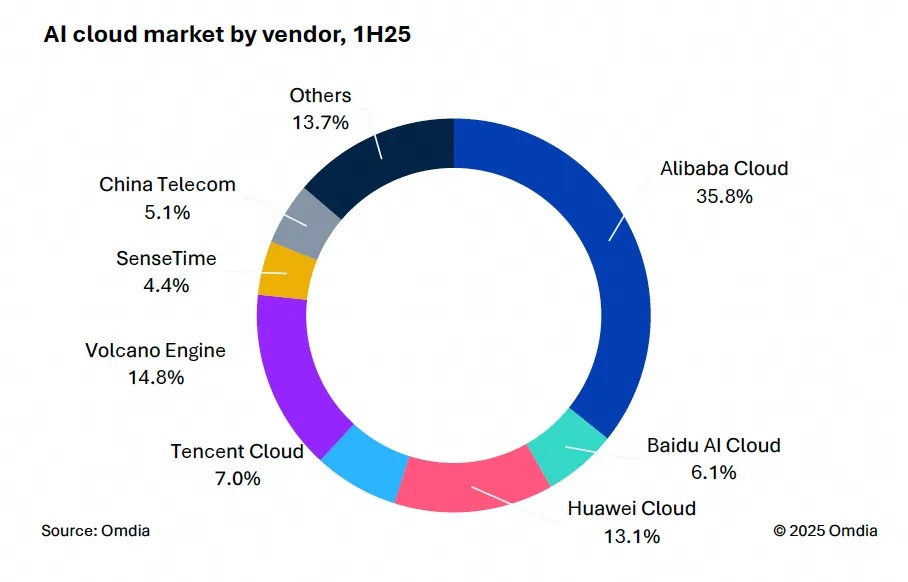

9į┬9╚šŻ¼ć°ļHÖÓ═■╩ął÷š{čąÖCśŗėóĖ╗┬³(Omdia)░l▓╝┴╦ĪČųąć°AIįŲ╩ął÷Ż¼1H25ĪĘł¾ĖµĪŻųąć°AIįŲ╩ął÷░ó└’įŲš╝▒╚8%╬╗┴ąĄ┌ę╗ĪŻ

9į┬24╚šŻ¼╚A×ķ└żņ`š┘ķ_Ī░ųŪ─▄¾w“ׯ¼ę╗Ų┴ĄĮ╬╗Ī▒╚A×ķIdeaHubŪ¦ąą░┘śI¾w“×╣┘ėŗäØ░l▓╝Ģ■ĪŻ

č┼±R╣■ū“╚šą¹▓╝═Ų│÷ā╔┐ŅŅ^┤„╩ĮČ·ÖCŻ¼Ęųäe╩ŪŲĮ░Õš±─żĄ─YH-4000║═äė╚”įŁ└ĒĄ─YH-C3000ĪŻ

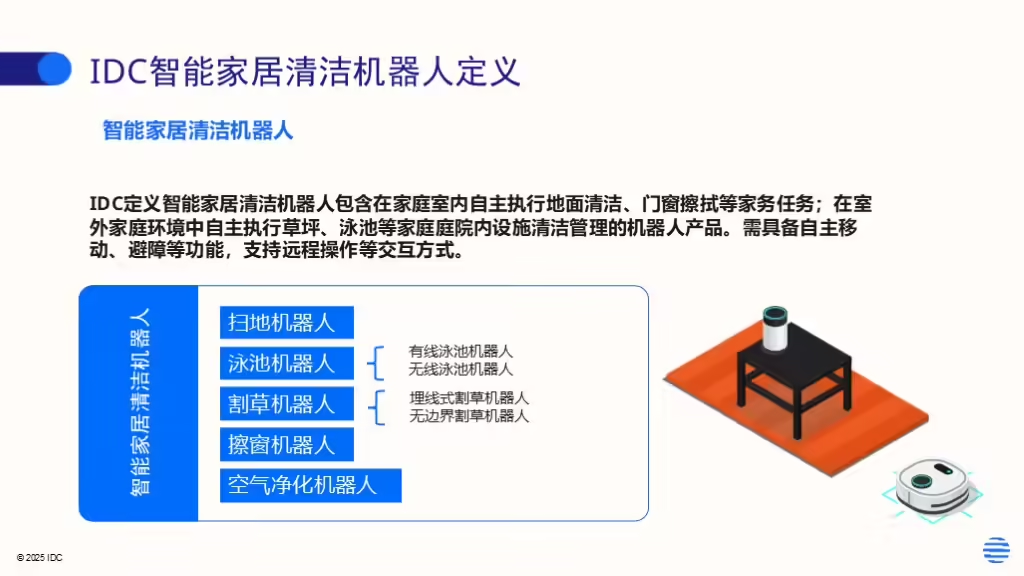

IDCĮ±╚š░l▓╝Ą─ĪČ╚½Ū“ųŪ─▄╝ęŠėŪÕØŹÖCŲ„╚╦įOéõ╩ął÷╝ŠČ╚Ė·█Öł¾ĖµŻ¼2025─ĻĄ┌Č■╝ŠČ╚ĪĘ’@╩ŠŻ¼╔Ž░ļ─Ļ╚½Ū“ųŪ─▄╝ęŠėŪÕØŹÖCŲ„╚╦╩ął÷│÷žø1,2╚f┼_Ż¼═¼▒╚į÷ķL33%Ż¼’@╩Š│÷ŲĘŅÉÅŖä┼Ą─╩ął÷ąĶŪ¾ĪŻ